Original Paper

# DESIGN AND IMPLEMENTATION OF VEDIC MULTIPLIER ON SPARTAN-6 FPGA USING VERILOG HDL

Hardik Modi<sup>a</sup>, Dharmendra Chauhan<sup>a</sup>, Sagarkumar Patel<sup>a</sup>, Vishva Gondalia<sup>b</sup>, Jayesh Khistariya<sup>b</sup>

<sup>a</sup> Associate Professor, Electronics and Communication Engineering Department, Chandubhai S Patel Institute of Technology, Charotar University of Science and Technology Changa, Anand, Gujarat, India hardikmodi.ec@charusat.ac.in

<sup>b</sup> Student, Electronics and Communication Engineering Department, Chandubhai S Patel Institute of Technology, Charotar University of Science and Technology Changa, Anand, Gujarat, India

#### ABSTRACT

Vedic Mathematics can rapidly conduct a several arithmetic operations. The multiplier unit is an essential part of general purpose and digital signal processors that greatly influences the processing speed. The Urdhva-Tiryagbhyam, a technique from Vedic math that makes it simple to multiply given integers as well, is utilized in this study to initiate a high-speed multiplier architecture. To determine product of two numbers, utilize the vertical and crosswise approaches referred to as Urdhva-Tiryagbhyam. Applying traditional Vedic mathematics, the paper discusses the creation of 2x2, 4x4, 8x8, 16x16, and 32x32 bit Vedic multipliers. The multipliers were synthesized and simulated using XILINX ISE Design Suite v.14.7 software. The multipliers were generated and defined using Verilog Hardware Description Language (VHDL).

#### **KEYWORDS**

Vedic Mathematics, Urdhva-Tiryagbhyam, Verilog, FPGA

# **1. INTRODUCTION**

A multiplication method named the Vedic multiplier was created in ancient Indian mathematics, particularly the Vedic scientific framework. The Vedic multiplier is one of the techniques used in Vedic arithmetic, which may be a collection of techniques and methods to perform quick mental calculations. In terms of actual applications, highly optimized duplicate calculations, like binary multiplication using hardware circuits, are used by sophisticated computerized frameworks and computers. [1] An arithmetic circuit or calculation that achieves duplication, particularly with binary integers, is known to be a binary multiplier. It receives two binary digits, frequently called the multiplicand and multiplier, and outputs their item. The majority of processes involve calculating several partial products, and then adding the results together. Although modified here, this procedure still performs lengthy multiplication on the base-tenth integrability but in this case, has been altered for usage with a binary number system. Instead of utilizing one adder to process each partial product, it began to be feasible to fit enough adders on just one chip to total all of the partial outcomes at once. Individually as more transistors per chip became possible as a result of large-scale integration. Instead of using it became feasible to fit enough adders on one chip to

complete all the partial products concurrently, as opposed to using a single adder for processing each part of the product independently. We may simulate and synthesize the design to get a digital circuit that performs multiplication using the Vedic approach by using the Vedic multiplier in Verilog HDL. When multiplication operations are necessary, this circuit can be integrated into bigger systems, such as processors or digital signal processing applications. It is significant to point out that additional efficiency and performance advancements can be made to the Verilog Vedic multiplier implementation through optimization like parallelism, pipelining, and the use of specialized hardware components like carry-save adders. Overall, the Vedic multiplier implementation in Verilog HDL provides a way to integrate classical mathematical techniques into modern digital systems and investigate different multiplication methods [1-65].

# **2. VEDIC MATHEMATICS**

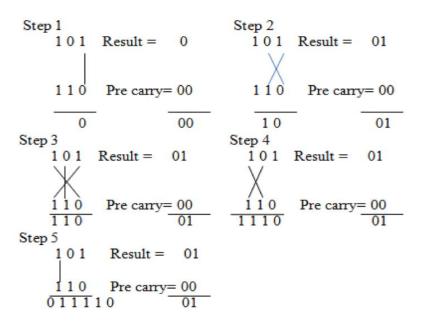

Carl Friedrich Gauss once said that mathematics is the "Queen of the Sciences." All sciences have their roots in math, which also serves as their foundation. The Veda is the source of Vedic mathematics, which offers a one-line, Very quick cross-checking, and issue resolution are both priorities [5]. The word "Veda," which originates from the Sanskrit word Vid and meaning "to know without limit," refers to all of the Veda-sakhas that are known to humankind. The Veda is a storehouse of all knowledge and, as one delves deeper into it, becomes more and more insightful. The idea of Vedic mathematics was reintroduced to this world by Sri Bharati Krishna Tirthaji. He created sixteen straightforward mathematical formulas known as thirteen sutras Corollaries or upsutras after studying the Atharva Veda in depth. The sutras' system is particularly straightforward and effective because it encompasses practically all areas of mathematics. The Sutras' application is entirely logical and sensible, even though it appears to be magic when arithmetic problems can be solved in one line faster. The sixteen sutras may efficiently do all basic operations, including subtraction, multiplication, addition, and division for any processor. In this case, we've used a multiplication method called Urdhva Tiryagbhyam. The 16 sutras, which assign a set of characteristics to a number or a collection of numerals, are the foundation of Vedic mathematics. In 16 Sutras (Phrases) and 120 phrases, the prehistoric Hindu mathematicians (Rishis) of Bharat outlined straightforward procedures for resolving all mathematical issues in two or three simple steps. In comparison to nowadays math, Vedic math helps a person solve math issues more quickly. Vedic math training has been discovered to help pupils solve difficult or simple mathematical issues by helping them make wise decisions and stay away from stupid mistakes. Vedic mathematics has been demonstrated to increase attention and decrease memory levels. allowing pupils to learn and improve their skills. It helps to improve logical thinking abilities and acquire a better comprehension of both fundamental and complex mathematical subjects. Crosswise is the most widely employed way in Urdhva Tiryagbhyam, which means vertically. [8] Urdhva Tiryagbhyam is applicable in all situations and can be applied to multiplying decimal and binary integers. The Urdhva Tiryakbhyam sutra's methods for multiplying two decimal integers illustrate the method in Fig. 1. The numbers at the end of the queue are multiplied, likewise, if a prior carry is present, It's also included. Any step that has been multiplied more than once is added to the preceding carry as well. The phrase "carry" for the following step is the tens place digit, while the term "result bit" refers to the unit place digit. Because sums and partial products are computed concurrently, processor clock frequency has no bearing on the multiplier. Microprocessors do not have to run at an ever-increasing frequency as a result, which maximizes their processing power. Its uniform structure makes it simple to arrange in a silicon chip. As a result, it is a technique that saves time, energy, and space as compared to multiplication in the classic sense.

Final answer of  $101 \times 110 = 011110$

Figure 1. Multiplication of two binary number using Urdhva-Triyagbhyam sutra[1]

#### 3. VLSI DESIGNS USING VEDIC MATHEMATICS

#### 3.1. Vedic Multiplier for 2x2 bit

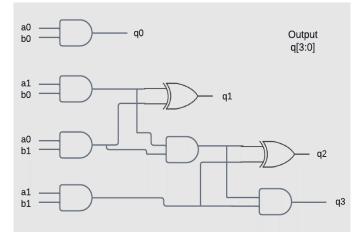

Figure 2 illustrates a 2x2-bit block diagram. [3] For a 2x2 bit Vedic multiplier, where b and a are input variables and a has input a0 and a1 and b has input b0 and b1, the first bit of output is found by multiplying a0 and b0, the second bit is created by adding the multiplication of b0, a1 and b1, a0, and the third bit is found by combining the carry from the previous operation with the multiplication of a1, b1 and the final bit is established by applying the carry discovered during the last summation process. Here, we have used 2 half-adders and a gate.

Figure 2: 2x2 bit block diagram [2]

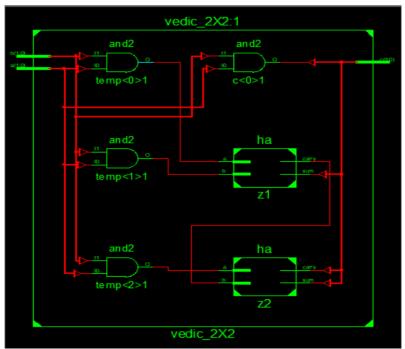

As illustrated in figure 3: Result of a 2x2 bit Vedic Multiplier, where b and a are the inputs and c is the four-bit output. So, at initially, both inputs are zero, so the output is also zero; then, if the input for a is 01 and the input for b is 11, the output is 0011. Similarly, if a's input is 10 and b's input is 11, the output will be 0110.

| Name           | Value | 10 ns  5 ns | 10 ns 15 ns | 20 ns 25 ns |

|----------------|-------|-------------|-------------|-------------|

| ► 😽 c[3:0]     | 0110  | 0000        | 0011        | 0110        |

| ▶ 📷 a[1:0]     | 10    | ( <u>op</u> | 01          | 10          |

| <b>b</b> [1:0] | 11    | 00          | X           | 11          |

|                |       |             |             |             |

Figure 3: Simulation result of Vedic Multiplier for 2x2 bit

Figure 4: RTL Schematic of 2x2 bit Vedic Multiplier

#### **3.2.** Vedic Multiplier for 4x4 bit

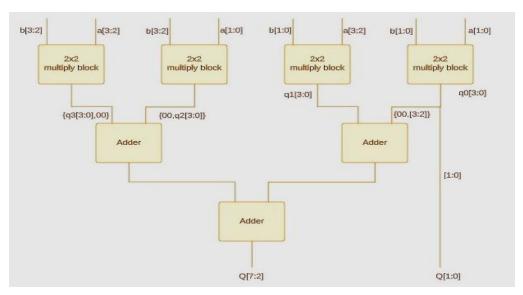

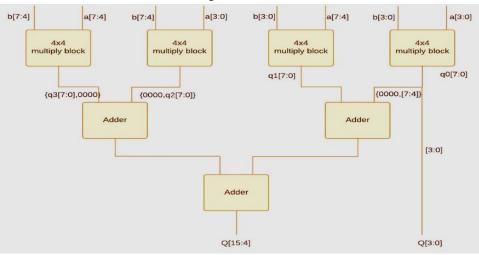

The suggested Vedic multiplier can be applied to shorten waiting times. Vedic multipliers with array multiplier structures are mentioned in early literature. [3] The configuration of Adders in Fig. 5 enables us to shorten the delay. It's interesting to note that the 4x4 Vedic multiplier module can have four Vedic multiplier modules of size 2x2. The final result is created by adding the outputs of 2x2 bit multipliers. The multiplier calculates the partial products and adds them using a 2x2-bit Vedic multiplier and adders before performing a 4x4-bit multiplication. Sections of the multiplication operation are performed, and the different outputs are combined and summed to get the final outcome. Here, a total of two 6-bit adders and one 4-bit adder are needed.

Figure 5: 4x4 bit block diagram [2]

As shown in fig 6: Result of a 4x4 bit Vedic Multiplier, where b and a are the inputs and c is the eight bit output. So, if the input for a is 0101 and the input for b is 1010, the output is 00110010. Similarly, if a's input is 1101 and b's input is 0100, the output will be 0110100. Figure 6: Simulation result of Vedic Multiplier for 4x4 bit

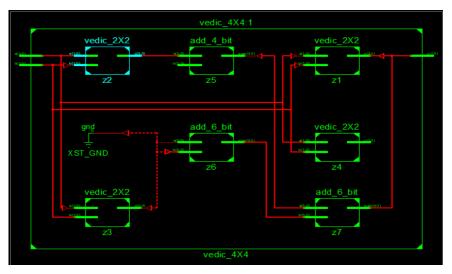

Figure 7: RTL Schematic of 4x4 bit Vedic Multiplier

We also implemented it on the Spartan 6 FPGA board. Here, we have used the FPGA board's input and output lines to provide the first and second inputs, respectively 1010 and 1110, and we are receiving an 8-bit output of 10001100.

Figure 8: FPGA Implementation of 4x4 bit Vedic Multiplier

#### **3.3.** Vedic Multiplier for 8x8 bit

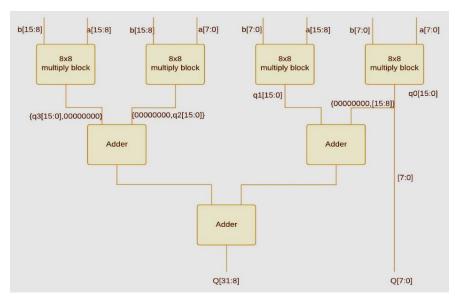

We used four Vedic Multiplier modules of 4x4 bit to create a Vedic Multiplier of 8x8 bit. As illustrated in Figure 9, a is divided into two halves, ah and al, while b is divided into two halves, bh and bl. As a result, combinations such as ahbh, bhal, blah, and albl are possible. This combination will be processed through a Vedic multiplier of 4x4 bit, and the output of the four Vedic multipliers will be passed via adders before arriving at a 16-bit output. The multiplier calculates the partial products and adds them using 4x4-bit Vedic multipliers and adders, which results in an 8x8-bit multiplication. The multiplying operation is broken down into stages, and the interim results are combined and added to get the end result.

Figure 9: 8x8 bit block diagram [2]

As shown in fig 10: Result of 8x8 bit Vedic Multiplier, where a and b are the inputs and c is the sixteen-bit output. So, if the input for a is 01010101 and the input for b is 10101010, the output is 0011100001110010. Similarly, if a's input is 01100111 and b's input is 11010100, the output will be 010101010101001100.

| Name        | Value            | 0 ns   | 5 ns       | 10 ns | 15 ns            |

|-------------|------------------|--------|------------|-------|------------------|

| ▶ 📷 c[15:0] | 0101010101001100 | 001110 | 0001110010 | 01    | 0101010101001100 |

| ▶ 📷 a[7:0]  | 01100111         | 01     | 010101     |       | 01100111         |

| ▶ 📷 b[7:0]  | 11010100         | 10     | 101010     |       | 11010100         |

|             |                  |        |            |       |                  |

Figure 10: Simulation result of Vedic Multiplier for 8x8 bit

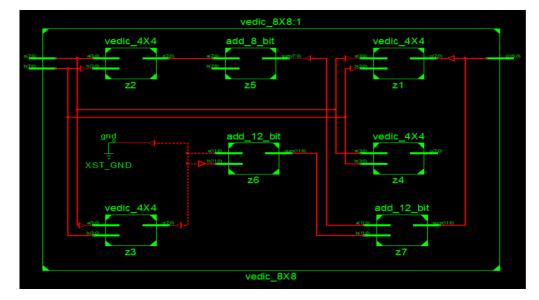

Figure 11: RTL Schematic of 8x8 bit Vedic Multiplier

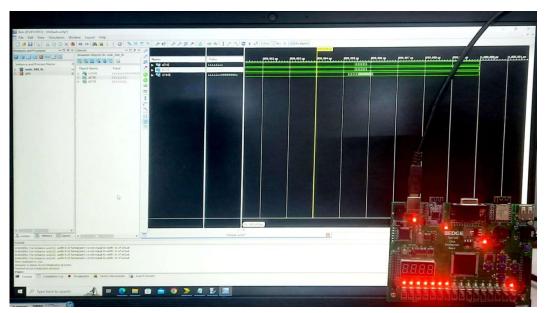

We also implemented it on the Spartan 6 FPGA board. Here, we have provided the first and second inputs of 8-bit from input and output lines of the FPGA board, respectively, and are receiving the 16-bit output. The first and second both inputs are 11111111 and the output we have received is 1111111000000001.

Figure 12: FPGA Implementation of 8x8 bit Vedic Multiplier

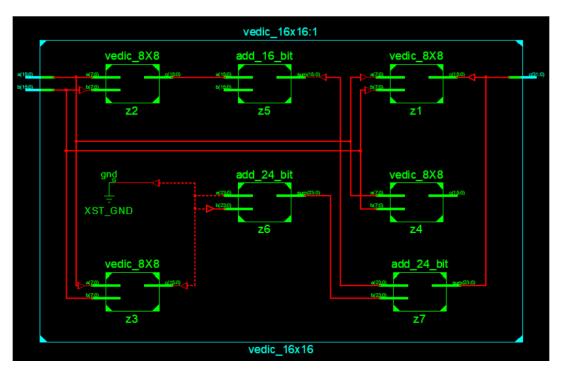

#### **3.4.** Vedic Multiplier for 16x16 bit

The multiplication utilizes the four-bit multiplier block to accomplish the fundamentals of Vedic multiplication, which have been discussed. The final result is created by adding the outputs of 8x8 bit multipliers. In order to determine the partial products and add everything together, the multiplier conducts a 16x16 multiplication using 8x8-bit Vedic multipliers and adders. The multiplication procedure is broken down into steps, and the intermediate outputs are combined and summed to produce the final output. As indicated in Figure. 13, a total of three adders—two 12-bit, and one 8 bit—are needed.

Figure 13: 16x16 bit block diagram [2]

As shown in fig 14: Result of 16x16 bit Vedic Multiplier, where b and a are the inputs and c is the 32-bit output. So, if the input for a is 1010101010101010 and the input for b is 0000111100001111, the output is 0000101000001001111101011111010. Similarly, if a's input is 010101010101010101 and b's input is 1111000011110000, the output will be 010100000100111110101111101000. Figure 14: Simulation result of Vedic Multiplier for 16x16 bit

Figure 15: RTL Schematic of 16x16 bit Vedic Multiplier

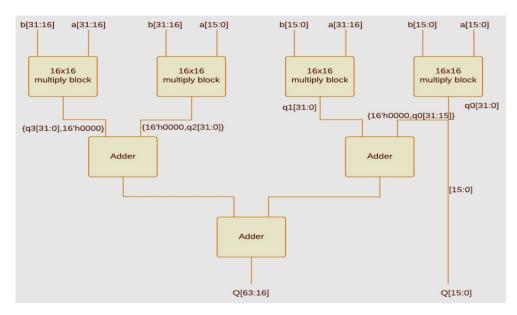

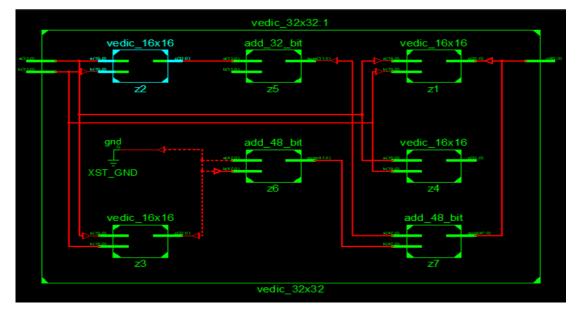

# 3.5. Vedic Multiplier for 32x32 bit

Four 16x16 Vedic multiplier modules can simply create a Vedic multiplier module for 32x32 bits. To create the final output, the outputs of multipliers of 16x16 bit are passed through adders in the appropriate order. The Vedic multiplication accomplishes efficient and feasible multiplication for big operands by segmenting the result of multiplication into smaller parts and effectively combining the partial results using adders. As indicated in Figure. 16, a total of two 48-bit and one 32-bit adders are needed.

Figure 16. 32x32 bit block diagram [2]

As shown in Figure 17: Result of 32x32 bit Vedic Multiplier, where a and b are the inputs and c is the 32-bit output. So, if the input for a is 32'h12345000 and the input for b is 32'h00001234, the output is 64'h0000014b60404000.

| Name        | Value                                   | 0 ns    | 2 ns                | 14 ns             | 6 ns            | 8 ns   |

|-------------|-----------------------------------------|---------|---------------------|-------------------|-----------------|--------|

| ▶ 📷 c[63:0] | 000000000000000000000000000000000000000 | 0000000 | 0000000000000000000 | 0100101101100000  | 010000001000000 | 000000 |

| ▶ 📷 a[31:0] | 0001001000110100                        |         | 00010010            | 0011010001010000  | 0000000         |        |

| Þ 📷 b[31:0] | 000000000000000000000000000000000000000 |         | 0000000             | 00000000000010010 | 00110100        |        |

|             |                                         |         |                     |                   |                 |        |

Fig 18: RTL Schematic of 32x32 bit Vedic Multiplier

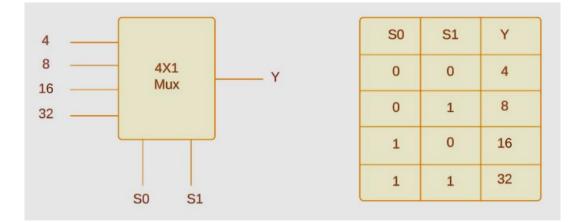

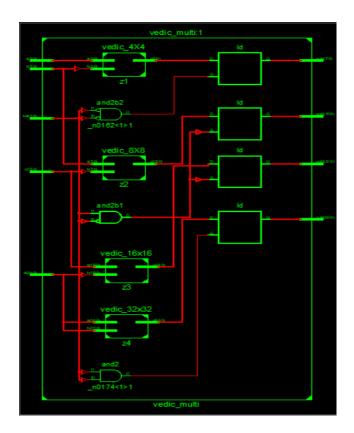

# 4. VEDIC MULTIPLIER USING 4X1 MUX FOR VARIABLE INPUTS BITS

We have created a Verilog code for the Vedic multiplier using 4x1 mux. There are therefore 4 inputs and 2 selection lines, and each selection line determines which input is sent on to the output. [10] As inputs, we have provided four different modules: the first input module is a 4x4 bit module, the second is an 8x8 bit module, the third is a 16x16 bit module, and the fourth is a 32x32 bit module. As depicted in Fig. 19, inputs will be called based on the selection lines. For example, if both S0 and S1 are zero, the module for 4x4 bits will be sent to the output, if S0 is 0 and S1 is 1 then the module for 8x8 bits will be sent to the output, the module for 16x16 bits will be sent to output when S0 is 1 and S1 is 0 and the module for 32x32 bits will be sent to output if S0 and S1 are both 1. This Vedic multiplier can handle up to 4 inputs of any number of bits; if we need to add more inputs, we can use a larger mux.

Fig 19: 4X1 Block Diagram

As shown in figure 20: Result of Vedic Multiplier, where d,c,b,a and sel are the inputs and out is the output. So, if the input for sel is 00 then module 4x4 is called and inputs a and b are used. Similarly, if sel is 01, 10, 11 then it will call module 8x8 which will use b and c inputs, 16x16 in which c and d inputs are used and 32x32 which has d as inputs respectively.

|                |                | 0.000 ns                                |                                         |                 |             |                                         |                   |                   |        |

|----------------|----------------|-----------------------------------------|-----------------------------------------|-----------------|-------------|-----------------------------------------|-------------------|-------------------|--------|

| Name           | Value          | 0 ns                                    | 100 ns                                  | 200 ns          | 300 ns      | 400 ns                                  | 500 ns            | 600 ns            | 700 ns |

| 🕨 🔣 out1[7:0]  | 01101110       |                                         |                                         |                 | 01101110    |                                         |                   |                   |        |

| 🕨 🔣 out2[15:0] | 00000000000000 | (000000000000)                          |                                         |                 | 1010        | 11010101110                             |                   |                   |        |

| 🕨 👹 out3[31:0] | 00000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |                 | 1001        | 11000000001000110                       | 11011010000       |                   |        |

| 🕨 👹 out4[63:0] | 00000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 00000000000000) | 00000000000 | 000000000000000000000000000000000000000 | 00100010010011011 | 00011101000100100 | 01     |

| 🕨 📷 a[3:0]     | 1010           | 1010                                    |                                         |                 |             | 0000                                    |                   |                   |        |

| 🕨 🍯 b[7:0]     | 00001011       | 00001011                                | 11111011                                |                 |             | 00000000                                |                   |                   |        |

| 🕨 👹 c[15:0]    | 00000000000000 | (000000000000)                          | 0000000010101                           | 1111000011110   |             | 00000                                   | 00000000000       |                   |        |

| 🕨 🚮 d[31:0]    | 00000000000000 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | 0000000000000   |             | 0000000000000                           | 00010111011011010 | 111               |        |

| ▶ 📷 sel[1:0]   | 00             | 00                                      | 01                                      | 10              |             |                                         | 11                |                   |        |

|                |                |                                         |                                         |                 |             |                                         |                   |                   |        |

Fig 20: Simulation result of Vedic Multiplier using 4x1 mux

Fig 21: RTL Schematic of Vedic Multiplier using 4x1 mux

# 5. ADVANTAGES

The key advantage of the Vedic multiplier is that it is faster than other multipliers because as the bit size grows, the area and delay grow gradually. For the previously mentioned 8x8, 16x16, etc. multipliers, the Vedic multiplier requires fewer gates, which results in extremely little power dissipation and minimal power consumption. Another benefit is in comparison to other multipliers, gate latency and area rise extremely gradually as the total amount of bits increases. The number of components used in the Vedic multiplier is reduced. As a result, it saves time and space. It provides the fastest speed of any conventional multiplier, as well as better throughput operations. When compared to other multipliers, the Vedic multiplier offers the largest benefit in terms of gate delays and structure regularity.

# 6. DISADVANTAGES

When there are high numbers, the system experiences carry propagation delay because of Urdhva-Tiryakbhyam architecture. Another drawback is that the propagation time in computing the RHS portion of the method also dramatically increases when the total amount of bits grows over 32 or 64 bits. Even the system itself gets complex when multiplying complex numbers.

# 7. APPLICATION

The rate of multiplication processes is critical in DSP. A form of technology called digital signal processing is used in almost all technical fields. It additionally represents the field of expertise that has advanced the fastest in the past ten years., posing enormous difficulties to the technical

sector. Rapid multiplication and addition processes are critical in DSP for Convolution, DFT, and Digital filters. It is utilized in the design of low-powered VLSI devices. It is also employed in frequency domain filtering (FIR and IIR), correlation, and digital image processing. Due to the fact that the great Vedic multiplication is quick, ALU employs this technique to provide consistent output. It is also used in real time signal.

# 8. CONCLUSION

The Vedic multiplier is one of the techniques used in Vedic arithmetic, which may be a collection of techniques and methods to perform quick mental calculations. In addition to enhancing accuracy, the goal of boosting speed and to decrease time, power, and processing latency. In Vedic mathematics, there are a total of 16 sutras, and we have used Urdhva Tiryagbhyam sutra, which means across and vertical from which we have created different modules of different bits for Vedic Multiplier. This paper shows Vedic Multipliers for various bits such as 2x2, 4x4, 8x8, 16x16, 32x32, and a Vedic Multiplier that is produced using a 4x1 mux utilizing a Verilog HDL that is only applicable to 4 inputs. Moreover, we implemented the 4x4 bit and 8x8 bit Vedic multipliers on the Spartan 6 FPGA board.

#### ACKNOWLEDGEMENTS

The authors would like to thank everyone.

# References

[1] Karthikeyan, S., & Jagadeeswari, M. (2021). Performance improvement of elliptic curve cryptography system using low power, high speed 16× 16 Vedic multiplier based on reversible logic. *Journal of Ambient Intelligence and Humanized Computing*, *12*, (pp. 4161-4170).

[2] Arpita A. Koli, S.B.Kulkarni (2015). Design of High speed Vedic MAC Unit using Urdhva Tiryakbhyam sutra & comparison with Conventional Architecture, *International Journal for Research in Applied Science & Engineering Technology (IJRASET)*, *3*, (pp. 818-828).

[3] Verma, P. (2012). Design of 4x4 bit vedic multiplier using EDA tool. *International Journal of Computer Applications*, 48(20), (pp. 32-35).

[4] Poornima, M., Patil, S. K., Shivukumar, S. K., & Sanjay, H. (2013). Implementation of multiplier using Vedic algorithm. *International Journal of Innovative Technology and Exploring Engineering (IJITEE)*, 2(6), (pp. 219-223).

[5] Verma, P., & Mehta, K. K. (2012). Implementation of an efficient multiplier based on vedic mathematics using eda tool. *International Journal of Engineering and Advanced Technology (IJEAT)*, 1(5), (pp. 75-79).

[6] Reddy, C. D. K., Reddy, S. R., & Murugan, C. A. (2022). Implementation of multiplier using Vedic mathematics. *Materials Today: Proceedings*, *65*, (pp. 3921-3926).

[7] Khubnani, R., Sharma, T., & Subramanyam, C. (2022, March). Applications of Vedic multiplier-A Review. In *Journal of Physics: Conference Series* (Vol. 2225, No. 1, p. 012003). IOP Publishing, (pp. 1-10).

[8] Tiwari, H. D., Gankhuyag, G., Kim, C. M., & Cho, Y. B. (2008, November). Multiplier design based on ancient Indian Vedic Mathematics. In *2008 International SoC Design Conference* IEEE, (Vol. 2), (pp. 65-68).

[9] Rudagi, J. M., Ambli, V., Munavalli, V., Patil, R., & Sajjan, V. (2011, November). Design and implementation of efficient multiplier using Vedic mathematics. In *3rd International conference on advances in recent technologies in communication and computing (ARTCom 2011)* IET, (pp. 162-166).

[10] Akhter, S. (2007, August). VHDL implementation of fast NxN multiplier based on vedic mathematic. In 2007 18th European Conference on Circuit Theory and Design IEEE (pp. 472-475).

[11] Shaik, S., Kanapala, S., Vijay, V., & Pittala, C. S. (2023). Design and performance analysis of low power and energy-efficient vedic multipliers. *International Journal of System Assurance Engineering and Management*, (pp. 1-9).

[12] Agarwal, A., Verma, J. P. N., & Srivastava, N. Design and Simulation of 16 Bit Vedic Multiplier using Urdhva Tiryakbhyam Algorithm, (pp. 543-551).

[13] Vucha, M. Design and FPGA Implementation of High Speed Vedic Multiplier. *International Journal of Computer Applications*, 975, 8887, (pp. 6-9).

[14] Murugesh, M. B., Nagaraj, S., Jayasree, J., & Reddy, G. V. K. (2020, July). Modified high speed 32bit vedic multiplier design and implementation. In 2020 International Conference on Electronics and Sustainable Communication Systems (ICESC) IEEE, (pp. 929-932).

[15] PRASAD, V. B., & RAO, B. S. (2020). Modified High Speed 32-bit Vedic Multiplier Design and Implementation, *In International Journal for Advanced Research in Science and Technology*,(pp. 39-44).

[16] M. Kivi Sona, V. Somasundaram, Vedic Multiplier Implementation in VLSI, Materials Today: Proceedings, Volume 24, Part 4, 2020, (pp. 2219-2230).

[17] Madhu Latha B. and Nageswar Rao B. (2014) 'Design and Implementation of High Speed 8-Bit Vedic Multiplier on FPGA', *International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering, Vol. 3, Issue 8,* (pp. 11601-11609).

[18] Yogeshwaran, K., Gowri, R., Sandhya, S., Reddy, T., & Vijayalakshmi, T. (2023, February). Design and Simulation of 16x16 Vedic Multiplier using Kogge-Stone Adder. In *2023 7th International Conference on Computing Methodologies and Communication (ICCMC)* IEEE, (pp. 452-457).

[19] Mala, F. A. (2023). Vedic Mathematics: A Mathematical Tale from the Ancient Veda to Modern Times: by Giuseppe Dattoli, Silvia Licciardi, and Marcello Artioli, World Scientific, 2021, (pp. 232).

[20] Singh, A., & Gupta, N. (2017). Vedic mathematics for VLSI Design: A review. *International Journal of Engineering Sciences & Research Technology*, (pp. 194-206).

[21] Tiwari, H. D., Gankhuyag, G., Kim, C. M., & Cho, Y. B. (2008, November). Multiplier design based on ancient Indian Vedic Mathematics. In *2008 International SoC Design Conference* IEEE, (Vol. 2), (pp. 65).

[22] M.Pushpa, S. Nagaraj, Design and Analysis of 8-bit Array, Carry Save Array, Braun, Wallace Tree and Vedic Multipliers, *IEEE Sponsored International Conference On New Trends In Engineering & Technology*(ICNTET 2018) (pp. 2687-2697).

[23] Anuradha, S., Meghana, R., Reddy, P. R. T., & Hemanth, P. FPGA IMPLEMENTATION OF 32 BIT VEDIC MULTIPLIER USING VERILOG HDL, *InGlobal Journal for Research analysis* (pp. 628-631).

[24] Pichhode, K., Patil, M. D., Shah, D., & Rohit, B. C. (2015, December). FPGA implementation of efficient Vedic multiplier. In 2015 International Conference on Information Processing (ICIP) IEEE. (pp. 565-570).

[25] Sudeep, M. C., & Vucha, M. (2014). Design and FPGA implementation of high speed vedic multiplier. *international journal of Computer applications*, *90* (pp. 6-9)

[26] Flake, P., Moorby, P., Golson, S., Salz, A., & Davidmann, S. (2020). Verilog HDL and its ancestors and descendants. *Proceedings of the ACM on Programming Languages*, 4(HOPL), 1-90.

[27] Mishra, S., Yadav, M., & Kesarwani, N. Implementation of Floating point Vedic multiplier by Urdhva Triyagbhyam using VHDL.

[28] Savji, A., & Oza, S. (2020). Design and implementation of Vedic multiplier. *International Journal of Recent Technology and Engineering (IJRTE)*, 8(6), 2277-3878.

[29] Chhabra, A., & Dhanoa, J. (2020, December). A Design Approach for Mac Unit Using Vedic Multiplier. In 2020 5th IEEE International Conference on Recent Advances and Innovations in Engineering (ICRAIE) IEEE. (pp. 1-5).

[30] Karthik, T. S., Manasa, K., & Raju, Y. D. S. (2021). Design and Implementation of 64 Bit High-Speed Vedic Multiplier. *INTERNATIONAL JOURNAL*, 6(1).

[31] Bianchi, V., & De Munari, I. (2020). A modular Vedic multiplier architecture for model-based design and deployment on FPGA platforms. *Microprocessors and Microsystems*, *76*, 103106.

[32] Chowdary, K. K. S., Mourya, K., Teja, S. R., Babu, G. S., & Priya, S. S. S. (2021, May). Design of Efficient 16-bit Vedic Multiplier. In 2021 3rd International Conference on Signal Processing and Communication (ICPSC) IEEE. (pp. 214-218).

[33] Akhter, S., & Chaturvedi, S. (2019, March). Modified binary multiplier circuit based on Vedic mathematics. In 2019 6th international conference on signal processing and integrated networks (SPIN) IEEE. (pp. 234-237).

[34] Kumar, A. S., Siddhesh, U., & Bhavitha, K. (2022, October). Design of High Speed 8-bit Vedic Multiplier using Brent Kung Adders. In 2022 13th International Conference on Computing Communication and Networking Technologies (ICCCNT) IEEE. (pp. 1-5).

[35] Chandrashekara, M. N., & Rohith, S. (2019, May). Design of 8 bit Vedic multiplier using Urdhva Tiryagbhyam sutra with modified carry save adder. In 2019 4th international conference on recent trends on electronics, information, communication & technology (*RTEICT*) IEEE. (pp. 116-120).

[36] Yaswanth, D., Nagaraj, S., & Vijeth, R. V. (2020, February). Design and analysis of high speed and low area vedic multiplier using carry select adder. In *2020 International Conference on Emerging Trends in Information Technology and Engineering (ic-ETITE)* IEEE. (pp. 1-5).

[37] Yadav, J., Kumar, A., Shareef, S., Bansal, S., & Rathour, N. (2022, August). Comparative Analysis of Vedic Multiplier using Various Adder Architectures. In *Journal of Physics: Conference Series* (Vol. 2327, No. 1, p. 012022).

[38] Hayum, A. A., Chinnapparaj, S., Sujatha, G., Selvi, G. T., Naved, M., & Mohanraj, P. (2021, April). Review of Vedic Multiplier Using Various Full Adders. In 2021 5th International Conference on Computing Methodologies and Communication (ICCMC) IEEE. (pp. 644-647).

[39] Anbumani, V., Soviya, S., Sneha, S., & Saran, L. (2021, November). Speed and power efficient Vedic multiplier using adders with MUX. In *2021 Innovations in Power and Advanced Computing Technologies* (*i-PACT*) IEEE. (pp. 1-5).

[40] Kaje, S. B., & Nayak, J. (2021). Design and FPGA Implementation of an Efficient 8× 8 Multiplier Using the Principle of Vedic Mathematics. In *Progress in Advanced Computing and Intelligent Engineering: Proceedings of ICACIE 2020* (pp. 749-761).

[41] Karuppusamy, D. P. (2019). Design and analysis of low-power, high-speed Baugh Wooley multiplier. *Journal of Electronics and Informatics*, 1(2), 60-70.

[42] Thangam, C., Ramaswamy, S., Karthikeyan, C., & Muthukumaran, N. (2022, April). Implementation of Barrel Shifter in Vedic Multiplier. In 2022 International Conference on Sustainable Computing and Data Communication Systems (ICSCDS) IEEE. (pp. 774-777).

[43] Dhanasekar, S., Bruntha, P. M., & Sagayam, K. M. (2019). An improved area efficient 16-QAM transceiver design using Vedic multiplier for wireless applications. *International Journal of Recent Technology and Engineering*, *8*(3),

[44] Gaur, N., Kapur, S., & Mehra, A. (2020, November). Application of vedic multiplier. In 2020 4th international conference on electronics, communication and aerospace technology (ICECA) IEEE. (pp. 234-237).

[45] Pasuluri, B. S., & Sonti, V. K. (2022, January). Design and Performance Analysis of Analog Filter and Digital Filter with Vedic Multipliers in Bio-Medical Applications. In 2022 International Conference for Advancement in Technology (ICONAT) IEEE. (pp. 1-8).

[46] Tripathi, D., & Wairya, S. (2021, June). An efficient QCA Vedic multiplier for nanotechnology applications. In 2021 International Conference on Intelligent Technologies (CONIT) IEEE.(pp. 1-6).

[47] Sudhamsu Preetham, J. V. R., Nethra, P., Chandrasekhar, D., Akhila, M., Arun Vignesh, N., & Panigrahy, A. K. (2022). Vedic Multiplier for High-Speed Applications. In *Communication, Software and Networks: Proceedings of INDIA 2022* (pp. 349-356).

[48] Verma, A., Khan, A., & Wairya, S. (2023). Design and Analysis of Efficient Vedic Multiplier for Fast Computing Applications. *International Journal of Computing and Digital Systems*, *13*(1), 190-201.

[49] Kumari, A., Kharwar, S., Singh, S., Mohammed, M. K., & Zaki, S. M. (2022, September). Design and Implementation of Modified Vedic Multiplier Using Modified Decoder-Based Adder. In *International Conference on Emerging Technologies and Intelligent Systems* (pp. 207-215).

[50] Penchalaiah, U., Umadevi, N., Chandupriya, P., Rishitha, P. N., Sindhuja, N., & Shareef, M. M. (2023). DESIGN AND IMPLEMENTATION OF MODIFIED VEDIC MULTIPLIER USING HSCG-SCG ADDER. *Turkish Journal of Computer and Mathematics Education (TURCOMAT)*, *14*(2), 454-463.

[51] Ande, B., Kalidindi, L. D., Mallula, P. K., Dantuluri, P. V., & Vegesna, N. (2022, January). High-Speed Vedic Multiplier Implementation Using Memristive and Speculative Adders. In 2022 International Conference on Computing, Communication and Power Technology (IC3P) IEEE. (pp. 186-189).

[52] Awade, A., Jain, P., Hemavathy, S., & Kanchana Bhaaskaran, V. S. (2021). Design of Vedic multiplier using reversible logic gates. In *Advances in Electrical and Computer Technologies: Select Proceedings of ICAECT 2020* (pp. 435-448).

[53] Lachireddy, D., & Ramesh, S. R. (2020). Power and delay efficient ALU using vedic multiplier. In *Advances in Electrical and Computer Technologies: Select Proceedings of ICAECT 2019* Springer Singapore. (pp. 703-711).

[54] Ram, G. C., Lakshmanna, Y. R., Rani, D. S., & Sindhuri, K. B. (2016, March). Area efficient modified vedic multiplier. In 2016 International Conference on Circuit, Power and Computing Technologies (ICCPCT) IEEE. (pp. 1-5).

[55] Kant, A., & Sharma, S. (2015, September). Applications of Vedic multiplier designs-a review. In 2015 4th International Conference on Reliability, Infocom Technologies and Optimization (ICRITO)(Trends and Future Directions) IEEE. (pp. 1-6).

[56] Bansal, Y., Madhu, C., & Kaur, P. (2014). High speed vedic multiplier designs-A review. 2014 Recent Advances in Engineering and Computational Sciences (RAECS), 1-6.

[57] Kumar, G. G., & Charishma, V. (2012). Design of high speed vedic multiplier using vedic mathematics techniques. *International Journal of Scientific and Research Publications*, 2(3), 1.

[58] Kunchigi, V., Kulkarni, L., & Kulkarni, S. (2012, March). High speed and area efficient vedic multiplier. In 2012 International conference on devices, circuits and systems (ICDCS) IEEE. (pp. 360-364).

[59] Kerur, S. S., Prakash Narchi, J. C., Kittur, H. M., & Girish, V. A. (2011). Implementation of Vedic multiplier for digital signal processing. In International Conference on VLSI, Communication & Instrumentation (ICVCI) (pp. 1-6).

[60] Pradhan, M., Panda, R., & Sahu, S. K. (2011). Speed comparison of 16x16 vedic multipliers. *International journal of computer applications*, *21*(6), 0975-8887.

[61] Gokhale, G. R., & Gokhale, S. R. (2015, December). Design of area and delay efficient Vedic multiplier using Carry Select Adder. In 2015 International Conference on Information Processing (ICIP) IEEE (pp. 295-300).

[62] Goel, A., Gupta, A., Kumar, M., & Pandey, N. (2017, October). Novel architecture for area and delay efficient vedic multiplier. In 2017 Recent Developments in Control, Automation & Power Engineering (RDCAPE) IEEE. (pp. 45-48).

[63] Priya, R., & Kumar, J. S. (2013). Implementation and comparison of vedic multiplier using area efficient CSLA architectures. *International Journal of Computer Applications*, 73(10).

[64] Pooja, V. G., Premananda, B. S., & Ramesh, G. S. (2018, May). Design of compact vedic multiplier for high performance circuits. In *2018 3rd IEEE international conference on recent trends in electronics, information & communication technology (RTEICT)* IEEE. (pp. 1168-1172).

[65] Singh, P., Dinendra, C., Hemanth, R. J., & Vivek, N. M. (2022, February). Design Of High-Speed Vedic Multiplier Using Urdhva Tiryakbhyam Sutra. In 2022 First International Conference on Electrical, Electronics, Information and Communication Technologies (ICEEICT) IEEE (pp. 1-5)